# Diseño y Construcción de la CPU del Equipo MULTIMAT del Sistema de Transporte Colectivo (METRO)

Luis Octavio López Leyva<sup>1</sup>, Juan Luis Díaz de León Santiago<sup>2</sup>, Cornelio Yáñez Márquez<sup>2</sup>

<sup>1</sup>Departamento de Redes de Cómputo, CET Walter Cross Buchanan

<sup>2</sup>Laboratorio de Reconocimiento de Patrones y Procesamiento de Imágenes del

Centro de Investigación en Computación

Instituto Politécnico Nacional

07738 México, D. F.

Tel. (52) 55 57296000 Ext. 56584

lopez\_leyva@latinmail.com

{jdiaz,cyanez}@cic.ipn.mx

#### RESUMEN

El propósito de este trabajo es presentar el rediseño de la tarjeta CPU del MULTIMAT, utilizando el microprocesador 80188, con el objetivo de aprovechar las bondades y ventajas que ofrece este chip, optimizando con esto el espacio y la funcionalidad. El MULTIMAT es un equipo que opera en las instalaciones del Sistema de Transporte Colectivo (Metro) en el Distrito Federal de México. El BIOS de la tarjeta incluirá algunas rutinas de entrada, salida y manipulación de datos; así como también algunos cambios necesarios en el sistema operativo, quedando para un trabajo posterior el desarrollo del conjunto completo de rutinas en lenguaje ensamblador que conformarán el nuevo BIOS y sistema operativo. Un aspecto muy importante que merece mencionarse, es que el nuevo diseño puede permitir eventualmente que el Sistema de Transporte Colectivo empiece a generar tecnología propia y terminar con la dependencia de la tecnologia francesa. Con este tipo de diseños y modificaciones podemos contribuir los mexicanos para que el país entre de lleno al desarrollo tecnológico a la altura de una nación desarrollada.

#### Palabras clave:

BIOS, CPU, Independencia tecnológica, Microprocesador 80188, MULTIMAT, STC-*Metro*.

## I. INTRODUCCIÓN

La tecnología mundial avanza a pasos agigantados producidos por los países del primer mundo, los cuales someten a los países subdesarrollados, como el nuestro, a una excecrable dependencia técnica, económica y social. Aprovechando esa dependencia, los grandes capitales someten y financian obras de gran trascendencia en países atrasados, como México.

Un ejemplo claro de ello, es el hecho de que Francia llevó a cabo, en el año de 1967, un gran proyecto en nuestra ciudad capital denominado "METRO". Participó financiando la obra, equipo e instalación del mismo y asegurando una estancia técnica hasta nuestros días. Esto trae beneficios en los desarrollos e infraestructuras de las megaurbes donde se implantan estos proyectos, pero también trae grandes rezagos económicos debido a los enormes intereses que se pagan, así como también en el

desarrollo tecnológico del propio país, ya que las compañías transnacionales ocultan sus desarrollos a tal grado que el personal es simplemente un operario. Por ejemplo, cualquier modificación, adaptación o ampliación a los equipos del Metro está supeditada a la compañía francesa, por los compromisos establecidos en los contratos.

El Sistema de Transporte Colectivo (METRO) es un organismo de servicio público descentralizado, cuya función principal consiste en transportar con seguridad, economía y eficiencia a más de 5 millones de usuarios diariamente en el Distrito Federal; cuenta con 11 líneas (1 a 9, A, y B) y es la columna vertebral de la transportación masiva en la Ciudad de México, capital de la República Mexicana. Para ello se cuenta con una estructura orgánica bien establecida: un consejo administrativo, una dirección general, un comité de servicio, 10 gerencias, 21 subgerencias y 62 jefaturas de departamento.

Una de estas gerencias, la de Instalaciones Fijas, se encarga de los equipos e instalaciones que permiten energizar las vías, y por consiguiente, de la circulación y control de los trenes con la más amplia garantía de seguridad; estos equipos se encuentran en las estaciones, túneles y puestos centrales.

gerencia está integrada por departamentos, entre los que se incluye el de Automatización y Control, el cual tiene a su cargo los sistemas electrónicos automatizados que regulan el tráfico de los trenes a lo largo de todas las líneas; está dividido a su vez en varias secciones: Señalización, Pilotaje Automático, Computadoras y Mando Centralizado; y cada una de ellas tiene su función específica que ayuda a cumplir con los objetivos del Sistema: la Sección de Señalización se entera e informa a las secciones de Mando Centralizado y Pilotaje Automático sobre los aspectos relacionados con el estado y situación de la línea; la Sección de Pilotaje Automático se encarga de actuar directamente sobre los trenes, indicándoles con qué velocidad deben avanzar de acuerdo con las informaciones que recibe de Mando Centralizado, que a su vez recibe órdenes de la Sección de

J. Díaz de León, G. González, J. Figueroa (Eds.): Avances en Ciencias de la Computación, pp. 300-318, 2003. © IPN, México 2003.

Computadoras. Esta última está interrelacionada con las demás secciones, a través del Sistema de Regulación Automático de Trenes, el cual permite disminuir el intervalo de cada tren y sus subsecuentes, respetando para ello las normas y parámetros de segundad establecidas.

El intervalo entre trenes puede verse afectado por incidentes menores o de consideración, que conducen el desequilibrio de la oferta y la demanda de los trenes programados a cada minuto en las horas de servicio.

Las acciones del Sistema de Regulación Automático de Trenes se observan a través de los tableros de control óptico (TCO), ubicados en el edificio del puesto central de control (PCC), donde se vigila la marcha ordenada de los trenes de cada línea; esta labor tiende a dificultarse con el aumento del número de trenes en circulación.

Para enfrentar lo anterior, se cuenta con un sistema de dos computadoras, el cual es redundante por seguridad, recibiendo ambas las informaciones, pero sólo una de ellas está conectada a la salida, para que cuando exista un problema, inmediatamente se conmuten y siempre exista servicio.

#### I.1 El Multimat

Uno de los sistemas automatizados del Metro es el llamado Mando Centralizado que consiste en un conjunto de medios que permiten regular la circulación de los trenes, así como el estado de la alimentación de tracción en las líneas. Estos medios están conectados en el Puesto Central de Control, y se encuentran a disposición del regulador, persona responsable de la operación. Entre estos medios existen los de intervención, que transmiten informaciones del PCC a las líneas o controles, y las fuentes de información, que envían informaciones de las líneas al PCC, a través del MULTIMAT (Sistema de Teletransmisión y Control de Tráfico de Trenes).

A continuación se describirá brevemente en que consiste una línea del metro, para así poder ubicar los sistemas Multimats, su importancia y aplicación. Una línea puede representarse como una trayectoria cerrada, donde circulan los trenes en un solo sentido uno tras otro con una distancia de seguridad de dos señales al alto espaciamiento, llamada sección tapón; dicha trayectoria puede medir 30 kilómetros o más, y en las horas de más afluencia pueden estar circulando hasta 42 trenes.

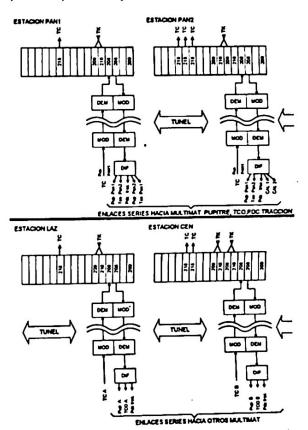

A lo largo de las trayectorias se encuentran colocados varios sensores cuyas señales son manejadas por los equipos de Multimat; estas señales informan el estado de la vía (semáforos, indicadores de velocidad, indicadores preventivos, circuitos de vía...) al PCC (Fig. I.1).

Otro aspecto muy importante que se transmite através de estos equipos es la conducción del Metro, con la ayuda del Sistema de Pilotaje Automático instalado en las estaciones y el del propio tren. Además, el sistema de Señalización se encarga de la seguridad de que todos los mandos sean correctos y bien establecidos.

Existen aproximadamente 35 equipos de Multimat para cada línea del Metro, ubicados en el PCC y en Estaciones. Los Multimats del PCC, ubicados en el TCO, Pupitre y PDC (puesto de despacho de carga) transmiten informaciones o comandos TC (telecomandos) a las Estaciones para realizar una acción determinada en el túnel de explotación, ya sea accionar un ruptor electromecánico, realizar una cambio de vía, o simplemente enviar alguna condición de seguridad.

Los Multimats de las Estaciones envían el control TK (telecontrol). de las acciones solicitadas. Cabe aclarar que dichos equipos reciben y transmiten simultáneamente.

Las comunicaciones a lo largo del túnel desde el PCC y Estaciones se lleva acabo con la ayuda de modems y las informaciones se distribuyen a través de difusores. La figura anterior muestra en forma muy representativa cómo están ubicados e instalalados los Multimats a lo largo de cada línea.

Los Multimats son básicamente computadoras industriales utilizados en sistemas de tiempo real y preparados para trabajar en condiciones extremas.

Figura I.1 Ubicación de los Multimats

Un equipo Multimat está construido con base en una tarjeta con un microprocesador y una tarjeta de bus ubicada al fondo del chasis, sobre el cual se conectan las tarjetas de entrada/salida.

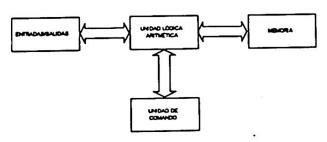

La tarjeta CPU contiene un microprocesador. Este sistema puede ser considerado como una estructura de cuatro unidades funcionales (Fig. I.2).

Figura I.2 Estructura funcional

La unidad aritmética y lógica tiene la función de ejecutar las instrucciones aritméticas y lógicas. La unidad de comandos tiene la función de realizar el tratamiento de otras instrucciones y asegurar el desarrollo correcto del programa. También maneja igualmente las señales de control y de sincronización necesarias para la transferencia de datos. De una manera general, estas dos unidades se reúnen físicamente en el interior del microprocesador.

La función de memoria contiene las instrucciones (constituyen el programa) destinado a ser ejecutado por el microprocesador y sus datos (o variables) sobre los cuales el programa va a operar. La función de entrada/salida juega el rol de aportar al microprocesador los datos o informaciones relativas medio exterior y viceversa.

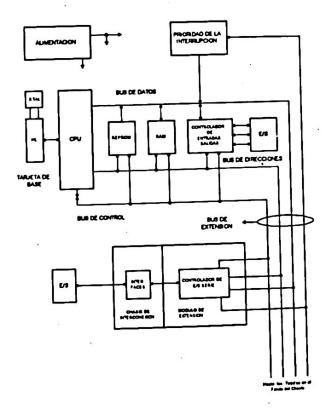

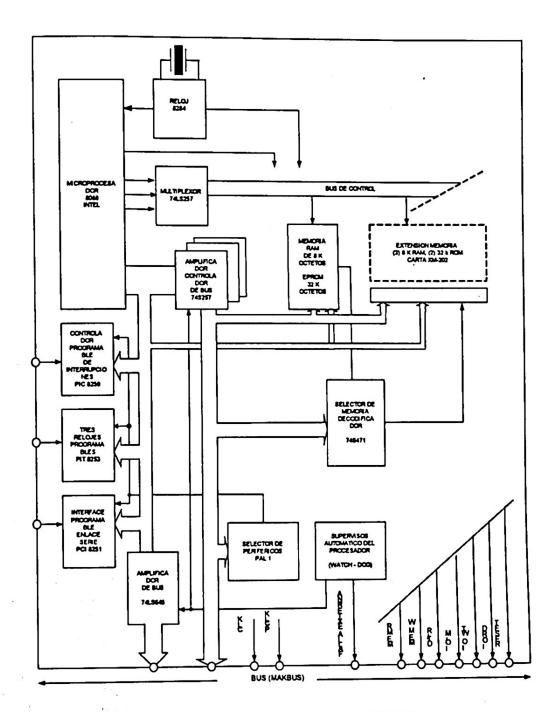

La Fig. I.3 muestra los bloques funcionales de la estructura general del equipo Multimat, enfatizando la Unidad de Procesamiento Central, tema de este trabajo.

## 1.2 Planteamiento del problema

Debido al envejecimiento y absolescencia de las partes que componen los sistemas, es cada vez más dificil proporcionarles mantenimiento, ya que existe un problema de reabastecimiento de refacciones proporcionadas por empresas extranjeras, las cuales son cada día más caras y no se encuentran en el mercado común. Por esta razón, se está intentando incursionar en el camino de la reingeniería; es decir, implementando equipos construyendo e fabricación nacional, apoyándose en proyectos dirigidos a ese fin.

En uno de estos proyectos se plantea la sustitución del Multimat, que es un equipo de origen europeo, por un equipo nacional. El Multimat comprende una unidad procesadora central (CPU) basada en el

8088 de Intel. microprocesador comunicación serie, tarjetas de 16 entradas digitales para el sensado de dispositivos de control externo, y tarjetas de 8, 24, y 40 salidas digitales para comandar la operación de dispositivos externos. En este proyecto se desarrollará tanto el hardware como el software del Multimat, con base en el microprocesador 80188 de Intel, que exhibe ventaias reales sobre el 8088.

Dada la complejidad que implica el desarrollar un sistema de esta magnitud, se tienen que marcar límites para ir cumpliendo metas a corto plazo. Por ello, en la primera etapa se trabajará solamente sobre la CPU, trabajo que se expone aquí.

Los trabajos estarán encaminados a la realización del hardware y software de pruebas para que funcione adecuadamente, así como también algunos ajustes en el sistema operativo de tiempo real necesarios para la adaptación de la CPU, quedando pendiente el desarrollo del hardware y software de las demás tarjetas que conforman este sistema, para realizarse en trabajos futuros.

Es decir, se pretende sustituir con tecnología nacional, como la primera etapa de un proyecto más ambicioso, la tarjeta procesadora central (CPU) de teletransmisión para el control de tráfico de trenes del STC-METRO (Multimat).

Figura I.3 Unidad Central de Procesamiento

La nueva CPU debe ser más barata, construida con componentes más accesibles, y cien por ciento compatible con la existente. Además, dado que es la primera etapa de un proyecto mayor que involucra a las demás tarjetas del Multimat, el nuevo diseño debe mantener el mismo tipo de bus, el mismo chasis, las demás tarjetas, el mismo tipo y niveles de alimentaciones, y debe ser capaz de soportar el software original para el control del tráfico de los trenes, realizando los cambios pertinentes en el sistema operativo propietario de la CPU del Multimat

## **II. ANTECEDENTES**

Para la explotación de las líneas del metro de la ciudad de México, existen sistemas automatizados que realizan funciones de mando y control a distancia de las condiciones que ocurren en las líneas en cada instante, lo que permite la óptima circulación de 282 trenes en las once líneas existentes, y son controlados a través del Mando Centralizado. Éste opera como un sistema nervioso del Metro, con las terminales nerviosas ubicadas a lo largo de las vías del tren, en las estaciones, en los patios de maniobras, y en las diversas instalaciones que hacen posible su operación. Las terminales son de dos tipos:

Los sensores, los cuales están relacionados con el tráfico y las condiciones generales de las vías, y captan la posición física y el movimiento de los trenes en estaciones y vías, así como cualquier anormalidad que se presente en la línea.

Los actuadores y disyuntores, que realizan las acciones de conexión e interrupción de circuitos eléctricos y electromecánicos, el movimiento de cambios en los rieles, la generación de señales para los semáforos y algunas acciones más, a partir de los mandos recibidos del Puesto de Central de Control (PCC) o bien de reguladores locales.

En cada estación existen equipos dedicados a concentrar y procesar las señales de los sensores, transmitiéndolas por un tipo de cable al Mando Central, del cual reciben también información para su distribución a los actuadores. Estos equipos de estación se conocen como PLC (programable logic controller), los cuales están constituidos por procesadores de 8 bits y tarjetas modulares de comunicación, diseñadas para operar en ambientes hostiles. Estos PLC's funcionan en sitios específicos de las estaciones, pero también en las estaciones rectificadoras de corriente, realizando funciones de transducción (transformación y adecuación) de señales, así como de control.

La estructura central del sistema de Mando Centralizado, está conformada por un equipo de teletransmisión Multimat (recepción-transmisión), que recibe y transmite información de las estaciones y a su vez las entrega o recibe de una unidad llamada

lógica de Mando centralizado, que a su vez alimenta a los Tableros de Control Óptico (TCO) del PCC y recibe comandos del *pupitre* para su distribución a las estaciones.

## II.1 Componentes del mando centralizado

La instalación central del mando centralizado se encuentra integrada por tres sistemas principales: el Sistema Base, el de Optimización, y el de Alarmas.

El Sistema Base está integrado por módulos que realizan las funciones de: tráfico, gestión de tráfico de trenes, tracción, gestión de la energía de corriente directa (que constituye la fuerza motriz y es suministrada por las subestaciones de rectificacón), tablero de control óptico, teletransmisión (constituido a su vez por los equipos de recepción, difusión, concentración y transmisión de señales a las estaciones y vías) y el pupitre de telemandos.

El módulo de tráfico está relacionado con la identificación y posicionamiento de los trenes a lo largo de la vía, y al igual que en el módulo de tracción, procesa las señales en las dos direcciones. Lo importante de este módulo es que tiene que ver con el movimiento de los trenes en las estaciones terminales, movimientos que implican el cambio de vías para iniciar un nuevo viaje en sentido contrario.

El módulo de tracción está relacionado con los estados de energización y desenergización en los diferentes tramos de la vía, como resultado de la apertura o cierre de los disyuntores y ruptores que operan los sistemas de alimentación de la corriente continua de 750 VCD.

Es importante señalar que los efectos de los mandos que este módulo tiene sobre los trenes, son tanto de tracción como de frenado, en tanto que la interrupción de corriente en el sistema de tracción del tren, dispara automáticamente un proceso de frenado.

El subsistema Tablero de Control Óptico forma parte del módulo de Telecontrol, facilitando la visualización de la línea, y constituye parte de la interfase hombre - máquina, que permite que el regulador tenga la información básica de los trenes y dispositivos para la operación de la línea, y además para verificar que sus mandos son correctamente ejecutados.

A través del TCO es posible conocer: la posición e identificación de los trenes, la presencia de tensión en linea y las fuentes de alimentación de la energía motriz, el estado de todos los dispositivos de control en las instalaciones de la línea y el estado de los indicadores de alarmas referentes a los diversos aspectos críticos de operación de la línea (como inundaciones de vías, cierre de puertas, iluminación de estaciones...).

El TCO está formado normalmente por varios paneles, que reciben la información correspondiente a zonas determinadas de la línea, desde los módulos

de tráfico, tracción, optimización y alarmas. Tiene usualmente asociados varios equipos de cómputo, que se encargan de procesar señales relacionadas con códigos y direcciones físicas en la línea a posiciones específicas de LED's en el tablero: normalmente se utilizan tres computadoras para controlar los paneles de cada TCO.

El subsistema Módulo de Teletransmisión realiza la adquisición de datos de las estaciones, donde son agrupadas y codificadas las señales para su transmisión vía modem al PCC, donde se reciben, decodifican y se difunden a los equipos de cómputo del TCO y de los diferentes módulos del sistema.

El Módulo de telemando es el sistema de activación y transmisión de las señales generadas por los reguladores (agentes encargados de la regulación) desde el pupitre, equipados con platinas (actuadores electromecánicos) y/o computadoras personales con pantallas táctiles. Normalmente las señales que se generan en el pupitre son bidireccionales, porque si bien los comandos deben ser ejecutados por los actuadores instalados a lo largo de la línea, el regulador debe recibir indicaciones que confirmen la transmisión de sus mandos.

El módulo de telemando incluye necesariamente diversos elementos transductores a cargo de las señales eléctricas que salen del pupitre para adecuarlas a los requerimientos y protocolos de transmisión a las estaciones, vía modems, fibras ópticas o en modo de hilo a hilo.

El Módulo de telecontrol contiene las componentes y la lógica para realizar el despliegue de señales de tipo luminoso (LED's) en el TCO formado por varios paneles con indicadores de tipo luminoso, que identifican a los trenes, e indican sus posiciones y estados a lo largo de la línea, así como los estados de las diferentes componentes que conforman y/o controlan las instalaciones fijas de la línea. Usualmente los paneles del TCO cuentan con algún equipo limitado de cómputo o procesamiento, que distribuyen las señales a los LED's.

El Sistema de optimización se apoya en la para regular Sistema Base, del información automáticamente el tráfico de los trenes a partir de programas preestablecidos, que dependen del día en que se opere (hábiles, festivo, etc.):

Las funciones más importantes que se realizan en este sistema, adicionales a las del Sistema Base, son: regulación del tráfico, de manera que la distribución de los trenes en operación responda a los requerimientos de la demanda programada; movimiento de trenes en las terminales y en estaciones con enlaces; identificación y seguimiento de trenes (numeración) y generación de Bitácora . (reportes y estadísticas).

La funcionalidad del módulo de optimización (Polígono de carga), es en realidad más compleja,

porque los tiempos entre trenes, dependen del número de éstos en operación, el cual varía de unos días a otros y de unas horas a otras, especialmente en los días laborables en los que el número de pasajeros se incrementa apreciablemente en los horarios de inicio y terminación de labores en fábricas, oficinas y escuelas.

#### II.2 Problemática

El mando centralizado presenta un grado de obsolescencia informática y tecnológica importante. la cual, aunada a la concepción cerrada de los sistemas informáticos, generan un punto crítico a resolver. Es inminente el mantenimiento de estos sistemas, los cuales se componen de elementos de software y hardware obsoletos.

El mantenimiento debe incluir toda una serie de acciones que debieran ser realizadas, para corregir algunos aspectos de funcionamiento deficiente e incluso riesgoso, que podrían llevar a situaciones de emergencia, a partir de dos causas o situaciones principales: falta de refacciones y salida del mercado. La falta de refacciones es debida en parte a que desde la instalación original no se contó con un lote suficiente de componentes, y además a que esas refacciones son muy difíciles de ubicar en el mercado hoy en día, por la obsolescencia de los equipos que Una buena parte de esas necesitan. las componentes deberán buscarse en mercados de segunda mano. La otra situación es la salida del mercado y desaparición de fabricantes de algunos equipos fundamentales como las computadoras GOULD, VAX, las pantallas táctiles, disco duros, impresoras, entre otros equipos, propicia que las refacciones de reemplazo sean aún más difíciles de consequir.

Una de las causas fundamentales de un buen número de los problemas actuales, radica en que cada uno de los sistemas de mando centralizado, fue entregado en su momento al Metro como un paquete tecnológico de llave en mano. Indiscutiblemente, en todos los casos, los niveles de funcionalidad, redundancia y segundad fueron incuestionables, pero característica una comparten determinadas reparaciones y adecuaciones sólo pueden ser realizadas en los sistemas actuales por el proveedor mismo, con costos mucho más altos, que los representados por una solución local.

## II.3 Detección de la necesidad

En septiembre de 2002 el Metro cumplió 33 años de servicio, y por efectos naturales del uso y el paso del tiempo, ha sufrido envejecimiento y obsolescencia de sus partes, pues cada vez va en aumento la incidencia de fallas y se hace más difícil el poder disponer de partes de repuesto. Esto provoca que se continúe con la dependencia tecnológica de empresas extranjeras, quienes han estado explotando económicamente a nuestro país.

Por todo esto, después de un estudio a fondo de la situación y con la firme intención de contribuir a mejorar las condiciones actuales, se llegó a la conclusión de resolver una de las tantas necesidades de automatización de dicho organismo.

## II.4 Selección del sistema.

Es precisamente dentro de la sección de mando centralizado donde se encuentra el sistema de teletransmisión para el control de tráfico, llamado Multimat, concebido de acuerdo con tarjetas de formato europeo, lo cual se desea sustituir.

Para resolver esta necesidad se analizaron varias alternativas de solución. Primero se pensó en adquirir un nuevo sistema de teletransmisión que fuera de tecnología de punta, y además de fabricación nacional, y por si fuera poco que garantizara su funcionamiento y mantenimiento: se buscó en el país dicho equipo y no se encontró proveedor mexicano que cumpliera con las características solicitadas; había quien decía tenerlo, pero se descubría que era equipo extranjero y se llegaba al mismo punto, por tal motivo se rechazó.

También se revisaron algunos acuerdos con instituciones educativas que pudieran realizar dicho proyecto. Se pensó en la Universidad de las Américas ubicada en puebla, el propio Instituto Politécnico Nacional, la Universidad de Morelos, la UNAM, el Tecnológico de Monterrey, y algunos otros. Al consultar algunas empresas privadas, éstas dijeron que sí. Sin embargo, en ese entonces ya existía la amarga experiencia de que a una empresa mexicana se le confió el proyecto de Simulación de la Regulación de Tráfico de Trenes del Metro, donde se le proporcionaria capacitación a los reguladores y conductores, resultando un fracaso, porque desde el momento en que se instaló, se encontraron muchas irregularidades e irresponsabilidades que trajeron como consecuencia que ese equipo hasta la fecha no funciona y se encuentra abandonado.

Las autoridades del Instituto Politécnico Nacional y el Sistema de Transporte Colectivo (Metro) firmaron un acuerdo para realizar reingeniería de tecnología nuestro proyecto pais, extranjera en inmediatamente pasó a manos del Centro de Investigación y Desarrollo de Tecnología Digital (CITEDI - IPN), ubicado el la ciudad de Tijuana Baja California. El CITEDI se concretó a seguir al pie de la letra las especificaciones hechas por su cliente, realizando así una réplica de cada una de las tarjetas que conformaban el sistema de teletransmisión Multimat. Además, se dio a la tarea de modificar y adecuar el sistema operativo de tiempo real MTR.

Aprovechando esta oportunidad de poder seguir los pasos de desarrollo tecnológico, en este trabajo de

tesis se decidió utilizar un microprocesador más avanzado de Intel y así poder modificar los recursos de software desarrollados para la CPU de Mutimat. De aquí nace la idea de trabajar paralelamente con la tarjeta procesadora central, con la inclusión de un microprocesador más adelantado al que tiene el Multimat; es decir, aprovechando las ventajas que presentan los microprocesadores más avanzados al 8088.

En el momento de la construcción de esta tarjeta, ya existía la familia Pentium I, II, III y IV de Intel, por lo cual sería lógico pensar en seleccionar el más avanzado, pero hay un detalle que lo impide: dado que el bus utilizado (Makbus) agrupa 20 líneas de direcciones, 8 líneas de datos, 37 de control, y 12 de alimentación, estas condiciones nos restringen a escoger un microprocesador que no rebase el número de líneas de direcciones y de datos, porque se quiere sustituir únicamente la tarjeta procesadora central (CPU) conservando el bus, la alimentación, el chasis, las tarjetas de entrada/salida digitales y el sistema operativo MTR de tiempo real.

Otra razón de mucho peso para mantener la idea de usar un microprocesador apropiado para el Makbus, fue que el software de explotación del sistema de regulación de los trenes está basado en un microprocesador de 8 o 16 bits de datos, por lo que nos sujeta a pensar en continuar con la misma idea de utilizar un microprocesador con esas características.

## II.5 Definición del concepto

De acuerdo con lo antenor, y después de un análisis minucioso y un estudio de los microprocesadores existentes que cubrieran el proyecto, las ventajas y desventajas que se pudieran presentar, se llegó a la conclusión de utilizár el microprocesador 80188 de Intel. Este microprocesador se ajusta a las necesidades planteadas anteriormente; es decir, que presenta un bus de direcciones de 20 bits, un bus de datos de 8 bits y además integra 7 dispositivos dentro de él: un generador de reloj, un controlador de programable, un generador interrupciones programable de estados de espera, dos canales de acceso directo a memoria(DMA) de alta velocidad a 2 temporizadores tres segundo, Mbvte por programables de 16 bits, un controlador de bus local, una unidad programable de selección lógica de periféricos y memoria. Con ello se ahorra espacio, consumo de corriente, dinero, y se hace más eficiente la programación, permitiendo así mayor facilidad de implantación, dado que su microcódigo es más compacto, que el del 8088.

Una vez tomada la decisión de utilizar el microprocesador 80188 de Intel como base en la construcción de esta tarjeta, el problema a resolver se define de la siguiente manera: sustituir la tarjeta

procesadora central de teletransmisión para el control de tráfico de trenes del STC-METRO, llamado Multimat, y que ésta sea cien por ciento compatible con la existente; manteniendo el bus, chasis, tarjetas, alimentaciones y software original.

## II.6 Selección del equipo y materiales

Para diseñar el software que permite elaborar e instalar un paquete de procedimientos de manejo del hardware se contó con una microcomputadora personal con el microprocesador Pentium II a 450 Mhz., el macroensamblador MASM versión 6,0, DJPP C++ ALLEGRO, y Turbo C de Borland, sistema operativo de tiempo real (MTR 186), acompañado del software necesario para el manejo de entada/salida a periféricos (IES 186), así como también el código estándar de tareas de puesta a punto y de supervisión del sistema de tareas que maneja el MTR 186, denominado RTD 186.

En cuanto a instrumentos de medición y seguimiento de señales, se utilizó un osciloscopio HP a 100 Mhz., un analizador de estados lógicos HP, fuentes de alimentación, multímetro, lector, simulador y quemador de memorias ROM.

Como se seleccionó el microprocesador 80188 de Intel, esto nos enmarca a trabajar con la misma familia. El diseño contempla el uso de varios circuitos integrados que van a colaborar en la formación del sistema que se quiere realizar.

En el momento de la construcción de la tarjeta, existía en el mercado el microprocesador 80188, 8259, 8251, memoria RAM 62256, memoria ROM 27512, 8288, 74LS573, PAL16L8, 74LS244, 74LS245, 1488, 1489, con sus respectivos manuales de operación. Por ello, se continuó con la compra y el estudio de los diferentes circuitos integrados, el manejo de los lenguajes de programación C, el macroensamblador MASM, sistema operativo MTR 186, RTD 186, IES 186 y la recopilación de la información necesaria.

#### III. DEFINICIÓN DEL MULTIMAT

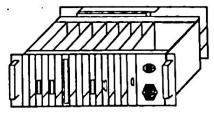

El sistema de TELETRANSMISIÓN PARA EL CONTROL DE TRÁFICO DEL STC-METRO denominado MULTIMAT, es una computadora de uso industrial, concebida para usar tarjetas de formato europeo, que utiliza como fondo del chasis metálico, un MAKBUS de Motorola (Fig. III.1).

Figura III.1 Chasis del Multimat

El chasís es un rack 3U/19 pulgadas que permite utilizar microprocesadores de 8 bits o de 16 bits en monoprocesador o multiprocesador; permite, por sus dimensiones europeas, recibir tarjetas con las siguientes medidas: ancho: 440 mm; altura: 132 mm y profundidad: 342 mm. Es capaz de recibir 16 tarjetas más la alimentación, y se le pueden administrar escuadras de fijación y manijas.

El Multimat incluye una unidad procesadora central (CPU) XM-200, basada en el microprocesador 8088 de Intel, y puede recibir 16 tarjetas de entrada/salida digital, más la alimentación.

Las tarjetas de entrada/salida que maneja el Multimat pueden ser muy diversas, tales como: la de 16 entradas digitales para el sensado de dispositivos de control externo, y módulos de 8, 24, y 40 salidas digitales para comandar la operación de dispositivos externos. Puede utilizar dos tipos de alimentación, ya sea de los módulos de alimentaciones que se integran en el chasis, o de una alimentación externa. También ofrece la posibilidad de implantarle el módulo de emergencia MAT 120, con un filtro sector y un contacto sector posterior con fusible.

A continuación se enlistan las especificaciones del Multimat:

Capacidad del chasis 16 ranuras

CPU Microprocesador 8088 a 5Mhz.

Extensión de memoria 2 bancos de RAM/EPROM

Comunicación serie 2 canales RS-232C

Entradas digitales 16 optoacopladas/relevadores

Salidas digitales 8/24/40 optoacopladores /relevadores/transistores

Fuente de alimentación + 5V a 20 A, - 5V, (+12V.,- 12V.) a

3A y 24V a 200 mA de comiente

directa

A continuación se presentará la CPU del Multimat original, y en la siguiente, se describirá el desarrollo de la nueva CPU, motivo de este trabajo de investigación y desarrollo tecnológicos.

#### **TARJETA CPU XM-200**

Presentación.- La tarjeta XM-200 se basa en el microprocesador 8088 de Intel y utiliza varios circuitos programables de la familia 82 de Intel. Reagrupa las funciones de la unidad central y permite la gestión de las memorias RAM/REPROM y de los controladores de entrada/salida, así como la administración de las tarjetas de entrada/salida en serie o paralelo.

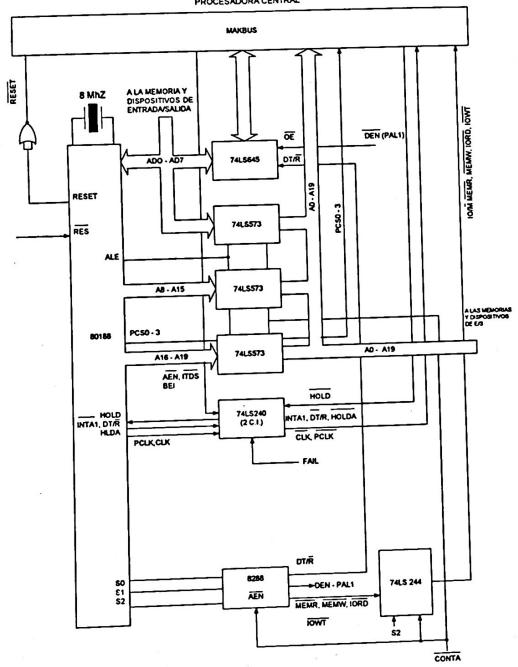

De acuerdo con la Fig. III.2, la CPU XM-200 posee los siguientes bloques funcionales:

Figura III.2

- Un microprocesador 8088 con sus circuitos de inicialización (8284).

- Una memoria RAM y EPROM (con posibilidad de extensión).

- Una interfase serie V24 síncrona/asíncrona (8251).

- Un controlador de interrupciones (8259).

## **CPU XM-200**

- Un contador/temporizadores programable de tres canales (8253).

- Una función (watch-dog).

- Un conector P0, que permite conectar a las tarjetas de entrada/salida necesarias para la aplicación.

Tres conectores permiten; (1) la conexión en el fondo del chasis metálico; (2) la unión a una consola de mantenimiento o de puesta a punto; y (3) la salida del mando perro guardián (watch-dog), y de la puesta a cero a distancia. Hay tres diodos de visualización en la cara delantera, los cuales indican varias situaciones: diodo rojo, tarjeta bajo tensión 5 voltios; diodo amarillo, estado del perro guardián (watch-dog) y diodo verde, presencia de una interrupción. Asimismo encontramos un interruptor momentáneo de inicialización (reset).

## Especificaciones.-

Procesador

Velocidad de procesamiento

Capacidad EPROM

Capacidad de RAM

Puerto serie

Temporizadores

Watch-Dog

8088

4.91 Mhz.

64/32Kbytes

16/32 Kbytes

1 RS-232C

3 de 16 bits

si

Watch-Dog SI Líneas de interrupción 8

Alimentaciones:

Circuitos 5 VCD 20 A., 5 VCD 3 A Manejadores RS-232C + 12 VCD y - 12 VCD

Inicialización.- La inicialización (o regreso a cero de todos los registros) de la tarjeta XM-200, se obtiene a la puesta en tensión, por medio del circuito RC (R3 y C4) la cual mantiene la señal RAZ (Reset del Switch Externo) a tierra durante 0.7 segundos. Sin embargo, es necesario que la señal RAZAUX (reset auxiliar que viene del sector de alimentación) sea falsa.

Alimentación y sistema de emergencia.- El sistema de emergencia de la alimentación al Multimat se realiza con la ayuda de la tarjeta MAT-120, la cual permite, en caso de corte sector, la salvaguarda del contenido de las memorias RAM y poder efectuar al regreso del sector, una reinicialización correcta de la operación.

Cuando la tarjeta XM-200 se encuentra en tensión y en funcionamiento normal, la salida de interrupción (RAZAUX) de la tarjeta MAT-120 se encuentra en un nivel lógico cero; si la tarjeta MAT-120 detecta una falla de sector superior a 2 ms. genera una interrupción. Esta tarjeta generalmente está cableada en la entrada no ocultable del CPU, lo que permite un tratamiento real de 3 ms.

Al final del tiempo antes determinado, se envía a la señal RAZDS a cero en el contacto A30 del conector P0 (quien aporta las alimentaciones necesarias para la tarjeta XM-200, así como también distribuye todas las señales útiles para la conexión a la tarjeta de entrada /salida), lo que permite realizar un reinicio a cero del sistema, en caso de reaparición del sector. El impulso de interrupción de falla sector permite al 8088 proteger sus registros y por lo tanto, reiniciar el

desarrollo de su programa en el lugar exacto en que fue interrumpido por la falla sector; sin embargo, es indispensable verificar que la tensión +5 V no descienda por debajo de 4.75 V antes del final de la interrupción.

Conexiones.- Incluyen los siguientes conectores:

- P0: Aporta las alimentaciones necesarias para la tarjeta, distribuye todas las señales útiles para la conexión a las tarjetas de entrada/salida.

- J1: Realiza la función de tipo serie V24 con una terminal de puesta a punto o de mantenimiento.

- J2: Permite el acceso a las señales WATCH-DOG y RAZAUX.

- J3: Sostiene al módulo de extensión de memoria.

También incluye los siguientes contactos para alambrar:

W0: Se relaciona a las interrupciones provenientes de P0 e interna de la tarjeta.

- W1: Se relaciona con las entradas del circuito que maneja las interrupciones así como con la señal NMI y permite la configuración REPROM 2764, 27128, 27256.

- ST1: Permite la opción watch-dog.

- ST2: Realiza la opción de memoria RAM socorrida.

- ST3: Permite la utilización de la señal FAIL.

- ST4: Por medio de una cadena de margarita (daisychain) se relaciona a la salida FAIL de una segunda tarjeta XM-200.

Organización de las zonas de acceso de los circuitos perféricos.- El espacio de las entradas/salidas (64 kbytes) se divide en dos partes distintas. La primera (0000H-7FFFH) se decodifica en la tarjeta XM-200 y permite dirigir los circuitos periféricos que se encuentren en ésta. La segunda (8000H-7FFFH) permite manejar las tarjetas periféricas entrada/salida externas a la XM-200 (Tabla III.1).

#### Periféricos:

{A15= 0 {tarjeta XM-200} {A15= 1 {tarjetas de E/S}

|           | CAPACIDAD<br>EN | ASIGNACION |                 |

|-----------|-----------------|------------|-----------------|

| DIRECCION | BYTES           | DE LAS E/S | DE LAS MEMORIAS |

| 00000     |                 |            |                 |

|           | 8 KBYTES        | BUS LOCAL  | MEMORIA RAM     |

| OIFFF     |                 | DE         | 8 Kbytes        |

|           |                 | LA TARJETA |                 |

|           |                 | XM-200     |                 |

|           | 24 Kbytes       |            | 200             |

|           |                 | 32 Kbytes  |                 |

| 07FFF     |                 |            | EXTENSION       |

| 08000     |                 |            | SEGÚN           |

|           |                 | ZONA DE    | LAS NECESI      |

|           |                 | LAS        | DADES           |

|           | 32 Kbytes       | TARJETAS   |                 |

|           |                 | DE E /S    |                 |

| OFFFF     |                 |            |                 |

|           |                 | ZONA LIBRE |                 |

| F8000     |                 |            |                 |

|           |                 |            | MEMORIA         |

|           | 32 Kbytes       |            | EPROM           |

|           |                 | ZONA DE    | 32 Kbyles       |

| FC000     |                 | MEMORIA    |                 |

|           | 6 Kbytes        | EPROMS     | MEMORIA EPROM   |

| FE000     |                 |            | 8 Kbytes        |

|           | 8 Kbytes        |            | MEMORIA         |

| FFFFF     |                 |            | EPROM 8 Kbyles  |

Tabla III.1 Configuración general de las zonas de memoria y de entrada/salida

| C.L.ó   | SERAL DE  | ZONA DE DIRECCION | DIRECCION DE   | DIRECCION DE    |

|---------|-----------|-------------------|----------------|-----------------|

| FUNCION | SELECCIÓN | SELECCIONADA      | CONTROL        | DATOS           |

|         | CSP1C     | 0000              | 00C0 IRR ISR   |                 |

|         | W C       |                   |                |                 |

|         | 1         | •                 | 00C1 Nivel IT  |                 |

| P1C     | 1         | 00C7              | 00C4 OCW 2,3   |                 |

| 8259    | l         |                   | 00C5 ICW1      |                 |

| INTEL   | 1         |                   |                |                 |

|         |           |                   | 00C2 IMR       |                 |

|         |           |                   | 00C3 OCW 1     | **              |

|         |           |                   | 00C6 ICW 2,3,4 |                 |

|         |           |                   | 0007           |                 |

| PIT     | CSPIT     | 0000              | 0008           | Contador 0 0000 |

| 8253    |           | •                 |                | Contador 1 0002 |

| INTEL   |           | 0007              |                | Contador 2 000  |

| USART   | CSPC1     | 0000              | OODA           |                 |

| 8251    |           |                   | •              |                 |

| INTEL   |           | 0007              | 0007           |                 |

| 8       | SETWD     | 00F0              |                |                 |

| WATCH   | (arme)    |                   |                |                 |

| DOG     | 1881 B.   | 00F7              |                |                 |

|         | RSTWD     | 00F8              |                |                 |

| WATCH   | (desarme) |                   |                |                 |

| DOG     |           | OOFF              |                |                 |

Tabla III.2 Zona de entrada/salida

Selección de circuitos periféricos:

Los circuitos (o funciones) que pertenecen a la unidad central y que utilizan las direcciones de selección son los siguientes (Tabla III.2):

- 1 Controlador de interrupciones programable (8259)

- 1 Interfase de comunicación programable (8251)

- 1 Interfase de tiempo programable (8253)

- 1 función de (watch-dog) de memoria

Su dirección de selección se obtiene con el arreglo lógico programable PAL2 10L8.

Zona de memoria.-Una zona de memoria está implantada dentro de la carta XM-200, equipada con dos conectores de 28 contactos, que pueden cada uno recibir cuatro tipos de memoria de 8 kilobytes de RAM estática y 8/16/32 kilobytes de ROM.

- -Memoria RAM estática de 8 kilobytes (TC5565)

- -Memoria REPROM de 8 kilobytes (2764)

- -Memoria REPROM de 16 kilobytes (27128)

- -Memoria REPROM de 32 kilobytes (27256)

El primer conector está implantado en la dirección 00000H, y el segundo en la dirección FFFFFH. La dirección de los circuitos de memoria RAM y ROM está dada de la siguiente manera: para la memoria RAM esta asignada la dirección 00000H hasta la dirección 01FFFH, que es igual a 8 kbytes, y la memoria EPROM está en la dirección FFFFFH, y según la capacidad de sus memorias 8/16/32 kbytes a la dirección FE000/FC000/F8000 (H).

Los módulos de extensión de memoria se pueden asignar en el espacio restante posible en el campo de dirección de un megabyte.

La capacidad total de memoria de la tarjeta XM-200 es de 200 Kbytes. Esta zona de memoria permite varias configuraciones (variadas en capacidad) y hace posible la elección de la dirección a partir de la cual existe la selección del módulo.

Ejemplos de configuraciones posibles:

48K RAM, 32K EPROM 24K RAM, 82K EPROM 8K RAM, 48K EPROM 8K RAM, 96K EPROM 8K RAM, 192K EPROM

Cuando la función RST está a nivel cero, o cuando la señal IO/M está en 1 (selección de las direcciones periféricas), esta EPROM no es seleccionada.

La CPU XM-200 está implantada con 8 kbytes (CSRAM) de memoria RAM y 32 kbytes de memoria REPROM., así como también tiene la capacidad para recibir a la tarjeta extensión de memoria XM-202, que se conecta en J3 y puede manejar 5 configuraciones diferentes:

| Opción 1 · | 8 KB RAM          | (CSMEM 0) |

|------------|-------------------|-----------|

| Opción 2   | 8 KB RAM          | (CSMEM 1) |

| Opción 3   | <b>8 KB EPROM</b> | (CSMEM 2) |

| Opción 4   | <b>8 KB EPROM</b> | (CSMEM 3) |

| Opción 5   | <b>8 KB EPROM</b> | (CSMEM 4) |

La señal MEMLOC determina trabajar con la memoria de la tarjeta XM-202, siempre y cuando esté en cero; y si está en 1, utiliza la memoria de la tarjeta de extensión de memoria XM-202.

La decodificación de las diferentes memorias se realiza gracias a la PROM TBP 28L22N.

## IV. DESARROLLO DE LA NUEVA CPU

Esta sección contiene la parte medular del articulo.

#### IV.1 Diseño funcional

Presentación.- Para el rediseño y desarrollo de la unidad procesadora central (CPU) se aprovecha la flexibilidad del bus (Makbus) de motorola instalado en el fondo del chasis; que permite utilizar microprocesadores de 8 o 16 bits en sistemas de monoprocesamiento o multiprocesamiento, así como las alimentaciones de voltaje y corriente necesarias para el buen funcionamiento de las tarjetas que maneja. También se aprovecha el software de aplicación, el sistema operativo utilizado en la CPU XM-200, y se adapta al microprocesador 80188.

Esta tarjeta presenta las siguientes características:

- Capacidad de administrar tarjetas de entrada/salida en serie o en paralelo.

- Tres conectores que permiten; (1) la conexión en el fondo del chasis; (2) la unión a una consola de mantenimiento o de acabado; y (3) la salida del mando watch-dog y de la puesta a cero a distancia.

- Tres diodos de visualización en la cara delantera, que indican:

- rojo: tarjeta CPU bajo tensión

- amarillo: estado del watch-dog

- verde: presencia de una interrupción

- 4. Un conector para extensión de memoria

- 5. Un interruptor momentáneo de inicialización.

- Además, presenta un sistema doble de protección. En caso de que se utilice la señal FAIL, todos los drivers de bus se colocan en tercer estado (alta impedancia), tanto en la tarjeta procesadora central como en y las tarjetas

periféricas de salida, con el propósito de proteger que no se manden datos erróneos.

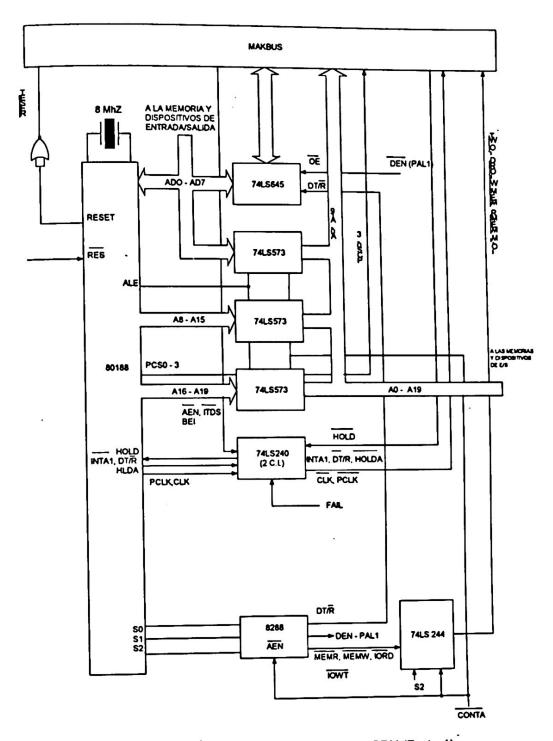

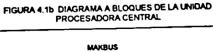

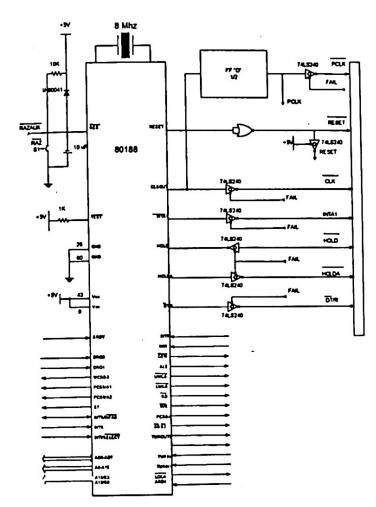

Bloques funcionales.- Las Figs. IV.1, IV.2 y IV.3 contienen el diagrama de la Unidad Procesadora Central, con los siguientes bloques funcionales:

- Un microprocesador 80188 de Intel, con capacidad de direccionamiento a memoria de 1 Mbyte y 64 kbytes de entrada/salida, que incluye internamente:

- Un microprocesador 8086-2 mejorado

- Generador de reloj

- 2 canales independientes de acceso directo a memoria (DMA)

- Controlador programable de interrupciones

- 3 temporizadores programables de 16 bits.

- Lógica programable de selección de memoria y periféricos.

- Controlador de Bus local

- Organización de Bus

- Una memoria RAM de 32K X 8 (62256) (con posibilidad de extensión)

- Una memoria EPROM de 64K X 8 (27512)

- Un controlador programable de interrupciones (8259)

- Una interfase serie V24 síncrona/asíncrona (8251)

- Un controlador de Bus (8288)

- Una función (watch-dog) de memoria.

- 4 módulos de RAM de 8k X 8 de extensión externa de memoria

- Un conector P0, que permite conectar a las tarjetas de entrada/salida necesarias para la aplicación.

#### Especificaciones de la nueva CPU.-

| Procesador                 | 80188 de Intel |

|----------------------------|----------------|

| Velocidad de procesamiento | 8 Mhz.         |

| Capacidad EPROM            | 64 Kbytes      |

| Capacidad de RAM           | 32 Kbytes      |

| Puerto serie               | 1 RS-232C      |

| Temporizadores             | 3 de 16 bits   |

| Watch-Dog                  | si             |

| Líneas de interrupción     | 10             |

| Allerantasianas            |                |

Alimentaciones:

Circuitos

5 VCD. 20 A., 5 VCD. 3 A

Manejadores RS-232C

+ 12 VCD. y - 12 VCD.

La nueva CPU está basada en el microprocesador 80188, con la configuración de modo mínimo. Este microprocesador tiene integrado un 8284 que proporciona una señal de reloj (CLKOUT), cuya frecuencia es la mitad del oscilador a cristal.

Figura IV.1

Nueva CPU (Parte 1)

Consideraciones sobre el nuevo diseño.- Antes de poder utilizar el 80188 con memoria o interfase de entrada/salida, hay que demultiplexar los buses. Los buses de direcciones y de datos en el 80188 están multiplexados para reducir el número de terminales requeridas en el circuito integrado.

Para demultiplexar estos buses se utilizan tres registros transparentes 74LS573 (Fig. 4.1b) para las conexiones AD0-AD7 del bus de direcciones y datos y las terminales de multiplexado A8-A15 y A16-A19. Estos registros transparentes, que son como alambres, siempre que la señal de habilitación (ALE) de dirección se vuelve 1 lógico transfiere las entradas

las salidas. Después de un corto tiempo, ALE regresa a 0 lógico, lo cual hace que los registros recuerden las entradas en el momento del cambio a un 0 lógico. En este caso recuerdan de A0-A7 en el registro inferior y A8-A19 en los dos registros superiores.

Esto produce un bus independiente para las terminales A0 a A19, que permiten que el 80188 direccione 1 megabyte de espacio de memoria. El hecho de que el bus de datos esté separado permite conectarlo con un dispositivo periférico de 8 bits,

Además, los circuitos 74LS573 proporcionan un aumento en las corrientes de salida de los registros a fin de que se puedan manejar más unidades de carga TTL; o un 0 lógico de salida proporciona hasta 32 mA. de disipación de corriente y una salida en un 1 lógico proporciona hasta 5.2 mA. de corriente. Una señal acoplada introducirá un retardo al sistema. Esto no produce ninguna dificultad, salvo que se utilicen memorias o dispositivos de entrada/salida.

que funcionan a la máxima velocidad del bus.

Nueva CPU (Parte 2) Figura IV.2

Los circuitos 74LS573 amarran las direcciones con la señal ALE, y permiten el paso de éstas con la señal CONTA, que a su vez depende de las señales AEN y FAIL. Esto quiere decir que cuando se presenta una falla se activa la señal FAIL y en consecuencia se deja de direccionar el sistema.

Figura IV.3 Nueva CPU (Parte 3)

El bus de datos es bidireccional, las ocho terminales del bus de datos D0-D7 emplea un registro octal bidireccional 74LS645, a este circuito llegan directamente las señales de los datos, por un lado del 80188, y por el otro del bus. DEN (PAL1) controla la dirección de los datos del 80188, que se refiere a la señal DT/R y se habilita y deshabilita con la señal DEN. La señal OE activa los datos hacia el bus, siempre y cuando no se estén accesando las memorias y dispositivos de entrad/salida locales.

El circuito integrado 74LS240 (Fig. 4.1.c) sirve para enviar y/o recibir señales de control al bus. Este circuito es un driver de tercer estado con histéresis, lo cual permite conectar un tercer estado a la señal FAIL, que viene del bloque watch-dog que anuncia

que ha existido una falla y su funcionamiento no está garantizado, con esto se aísla el bus con las tarjetas periféricas. Todos los drivers de bus se colocan en tercer estado (alta impedancia) tanto en la tarjeta procesadora central como en las tarjetas periféricas de salida, con el propósito de proteger que no se manden datos erróneos.

Además, se cuenta con el circuito integrado controlador de bus (8288), que genera las señales de control para lectura/escritura a memoria (MEMR, MEMW), y para lectura/escritura a puertos (IORD, IOWT); a él llegan las señales S0 a S2 que son las señales encargadas de hacer la transacción de información de bus. También a este circuito le llegan las señales de AEN, DEN, CLK.

A la señal AEN del 8288 le llega la señal CONTA del PAL2 que permite la habilitación de los comandos de salida del 8288 y con ello el control de las señales DT/R y DEN; estas señales controlan la dirección y habilitación de datos del 74LS645 hacia el bus.

Existen dos situaciones en las que las salidas no pueden ser habilitadas: la primera situación es cuando se están accesando las memorias y dispositivos de entrada/salida locales; y la segunda, es cuando existe una falla interna. En ambas situaciones, también se bloquearán los habilitadoeres de salida (OE) de los tres circuitos integrados 74LS573, los cuales manejan el bus de direcciones. Como las tarjetas externas están implementadas con la señal IO/M del microprocesador 8088, y dado que

la señal IO/M del microprocesador 8088, y dado que este microprocesador no maneja directamente esta señal, fue necesario obtenerla a-través de la señal de estado S2 del microprocesador 80188. La cual informa si se está accesando externamente a un periférico de I/O ó a una memoria.

Las señales de control MEMR, MEMW, CLK, PCLK, IORD, IOWR y IO/M, necesarias para controlar el flujo de información entre la unidad procesadora central y las tarjetas externas periféricas de entrada/salida van directamente al C.I. 74LS244 (Fig. 4.1d) para que les proporcione la corriente y voltaje adecuado, ya que éstas están conectadas al bus externo.

## IV.2 Periféricos

Dispositivos de entrada/salida de la CPU.-

Periféricos internos al 80188

El MPU 80188 tiene 64 Kbytes de direcciones para utilizarse como entrada o salida.

La familia IAPX 186, 188 incluye seis dispositivos integrados, junto con las unidades de interfase de bus y de ejecución (BIU y EU):

La unidad de selección de dispositivos

Generador de estados de espera;

Controlador de interrupciones;

Controlador de acceso directo a memoria

La unidad de temporización

## El controlador de bus local y Generador de reloj

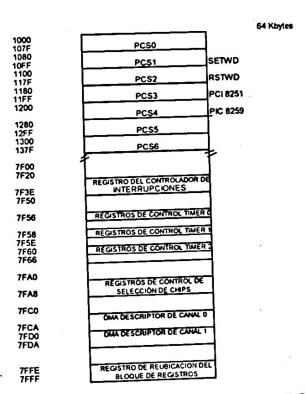

Los primeros cuatro de ellos son programables. El controlador de bus local y el generador de reloj operan de modo transparente al operador. Todos los periféricos internos son controlados por un conjunto de registros ubicado en el bloque de control de periféricos (PCB). El PCB es un conjunto de 256 registros ubicados en el E/S o espacio de la memoria. Siempre que el 80188 se reinicializa, el periféricos control de bloque de automáticamente colocado en la parte superior del mapa de E/S (direcciones E/S FF00H-FFFFH). El registro de reubicación del bloque de registros de control despierta con el valor 20FFH; ubicado en el área de direccionamiento de entrada/salida, en la para la necesaria dirección 7F00H. reubicación adecuada a las necesidades de esta tarjeta.

Cabe aclarar que la tarjeta XM-200 original tiene separado los periféricos utilizados dentro de la CPU en la dirección de entrada/salida de 0000H - 7FFFH y las tarjetas externas y sus periféricos están ubicados en las direcciones de entrada/salida 8000H-FFFFH.

Respetando este lineamiento, la unidad procesadora ubicará los periféricos internos de la CPU dentro del margen de dirección de entrada/salida 0000H-7FFFH y las tarjetas externas en la dirección entrada/salida 8000H-FFFFH.

Queda pues, ubicar los circuitos integrados periféricos de la CPU que no estén dentro del microprocesador 80188. En este caso utilizaremos la habilidad que nos presenta este micro para seleccionar dispositivos periféricos (o puertos). El 80188 genera 7 selectores de dispositivos con un rango fijo de selección de 128 bytes. Esto significa que cada línea de selección puede habilitar 128 posibles periféricos. Para esto se tomaron 4 selectores independientes para seleccionar los 4 diferentes dispositivos periféricos internos a la Unidad Procesadora Central.

## Periféricos internos de la CPU.-

a) Puerto serie 8251 USART de Intel. Circuito integrado complejo programable que nos sirve para comunicamos en serie en formato síncrono ó asíncrono, permitiendo programar para transmisión asíncrona, la velocidad de transmisión, el tamaño de la palabra de información, el número de bits de paro y tipo de paridad, transmisión duplex completo, con buffers en la línea de transmisión serie y en su puerto paralelo. Este circuito se conecta a los circuitos drivers son 1489 gue 1488 У integrados condicionadores de la señal RS 232C.

b) Controlador de interrupciones 8259 de Intel circuito integrado complejo programable que maneja 8 niveles de interrupción o peticiones de interrupción. puede conectarse en cascada para obtener hasta 64 niveles de interrupción, se programa por software como un periférico de entrada/salida. Los modos de prioridad pueden ser combinados o reconfigurados dinámicamente en cualquier momento del programa. c) Guardian del sistema (Watch-Dog).

de supervisar función la Tiene funcionamiento del sistema, previniendo errores. Cuando ocurre un error de algún circuito que perturbe el funcionamiento del sistema, este circuito activa la Interrupción No Mascarable (NMI), la cual realiza la función de inicializar el sistema (reset por software).

Decodificación de los dispositivos de entrada / salida.- Para seleccionar un dispositivo de entrada/salida de la unidad procesadora y que son internos al microprocesador 80188, basta con direccionar el mapa de registros internos (Fig. IV.4) ubicados en las direcciones 7F00H-7FFFH, y desplazarse a la dirección deseada.

Figura IV.4 Dirección de los dispositivos de E/S

Pero cuando se requiere seleccionar un dispositivo o función de entrada/salida que no se encuentre dentro del microprocesador 80188, pero si en la tarjeta procesadora central, se aprovecha la facilidad que nos da este microprocesador; el uso de uno de los 7 canales de selección de dispositivos que nos proporciona la unidad de selección de chip PCS0-PCS6.

Para seleccionar el C.I. 8259 que se encuentra en la unidad procesadora central, fuera del microprocesador, se utilizó la señal de selección de periférico PCS4. Para seleccionar el C.I. 8251 que se encuentra en la misma situación que en el anterior, se utilizó la señal PCS3. Lo mismo sucede para seleccionar la dirección de la función SETWD, se utilizó el PCS2. Finalmente para ubicar la dirección de RSTWD se utilizó la señal PCS1.

## IV.3 Memoria

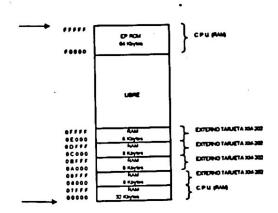

El microprocesador proporciona las señales de UCS (selección de memoria alta), utilizada para seleccionar los 64kbytes de la memoria ROM; (27512), LCS (selección de memoria baja), para manejar los 32 kbytes de memoria RAM (62256). proporciona señales cuatro También seleccionar diferentes espacios de memoria media, en cualquier parte de la memoria dentro de un Mbyte. En el nuevo diseño se aprovechará la habilidad de la CPU original para anidar una tarjeta externa XM-202 que, a su vez, puede manejar tres bloques de memoria RAM de 8 kbytes, y dos bloques de memoria ROM de 32 kbytes.

Al respecto cabe aclarar lo siguiente: la CPU XM-200 tiene una memoria RAM de 8k X 8 bytes, y una ROM de 32 kbytes; la nueva unidad procesadora central cuadruplica el espacio de memoria RAM, así como también duplica el espacio de memoria ROM, y además, aprovecha las señales directas de memoria media proporcionadas por el microprocesador 80188, para aceptar cuatro módulos más de memoria RAM de extensión externa de 8 kbytes, como se ilustra en la figura IV.5.

Los espacios de memoria externa quedan definidos

en las siguientes direcciones:

Figura IV.5 Mapa de memoria

Cada una de las memorias serán accesadas cuando se selecciona una señal de memoria y que además la señal CEN esté en bajo. Esto quiere decir que la señal CEN está en alto, cuando se esté accesando una memoria interna a la CPU o un dispositivo periférico también interno o que exista una falla en el sistema. Cuando la señal CEN está en bajo, garantiza que se puede acceder una memoria o periférico externo a la tarjeta procesadora, siempre y cuando sean activados con las señales MEMR, MEMW, IOWT, IORD proporcionados por el controlador de bus (8288).

## IV.4 Arreglos Lógicos Programables (PALs)

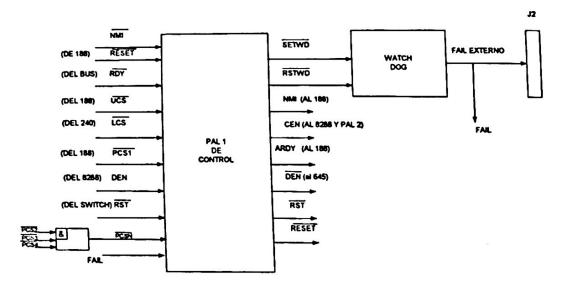

En esta sección se proporcionan las ecuaciones lógicas necesarias para controlar el sistema en su totalidad, para tal efecto, fue necesario utilizar dos circuitos de arreglo lógico programable PAL 16L8, el cual permite 16 entradas y 8 salidas.

Se utilizó el programa PALASM4 para programar el PAL 16L8 de control de la CPU, se crearon y generaron los archivos Logcon.pds, Logcon.xpt, Logcon.ldc, Logcon.jed, Logcon.hst y Logcon.trf.

Los archivos con extensión .pds corresponden a los archivos de diseño fuente. En ellos se define la entrada y salida al dispositivo empleado, las ecuaciones booleanas, y se pueden generar vectores de simulación para verificar las ecuaciones.

#### **ECUACIONES DEL PAL1**

NMI = NMI

CEN = !UCS # !LCS # !PCS1 #!PCSN # FAIL

ARDY = !RDY\*CEN DEN = !FAIL\* DEN RST = !RST (SWITCH)

RESET = RESET SETWD = IPCS1 RSTWD = IPCS2

En la PAL1 se generan 8 señales de control para esta tarjeta (Fig. IV.6), se muestran las entradas y salidas de este dispositivo.Las salidas generadas son: NMI, CEN, RDY, DEN, RST, RESET, SETWD, RSTWD. La señal NMI está conectada directamente al circuito supervisor del buen funcionamiento del software y hardware de la tarjeta (watch-dog), ya que cualquier situación anómala activa la interrupción no mascarable del 80188, la cual realiza la función de inicializar el sistema (reset por software). La señal CEN se activa en alto y mientras se mantiene en este estado quiere decir que ninguna memoria RAM, ROM o periférico interno a la tarjeta procesadora se está accesando y que además no exista falla.

La señal RDY activa en alto, se utiliza para sincronizar memorias o dispositivos de entrada /salida lentos, insertando ciclos de espera para extender su duración.

Figura IV.6

PAL de control de la CPU

La señal RDY pin, B27 del bus, el cual viene de las tarjetas periféricas. Si esta señal está en nivel bajo y la señal CEN en alto, entonces solicita tiempo para determinar la transferencia con el dispositivo de entrada/salida externo.

La señal DEN será activa a nivel bajo, siempre y cuando no exista falla en el sistema y se tenga la señal DEN en alto, proporcionada por el controlador de bus 8288. La señal DEN va directamente conectada al habilitador de salida (OE) del 74LS645 para permitir el paso de los datos al bus.

La señal RST, simplemente inicializa el sistema y se activa en nivel bajo, ya que este viene directamente del switch y su temporización o través del circuito RC.La señal RESET, se utiliza para realizar un reset interno, y viene de la señal RESET interna.

La señal SETWD es una función supervisora a través de la cual verifica el tiempo de ejecución de un cierto programa, éste revisa que todo el sistema funcione adecuadamente según lo planeado. Su activación se realiza a través de un dato en un puerto del espacio de entrada/salida y es seleccionando por la señal PCS1, activada en bajo.

La señal RSTWD es una función que inicializa el sistema por software, cuando existe alguna anomalía dentro de éste, también se selecciona un puerto del espacio de entrada/salida con la señal PCS2 activada en bajo.

## **ECUACIONES DEL PAL2**

DRQ0 = DMA0 # !LOCK DRQ1 = DMA1 # !LOCK DRQ0 # DRQ1 CS 8251= IPCS3 CS 8259= IPCS4

HOLDA= HOLDA

CONTA= !HOLDA \* !FAIL # CEN

La señal HOLD indica que el procesador esta solicitando el control de bus local para poder acceder a la memoria o un dispositivo periférico de entrada/salida. Para que no haya solicitud del bus local la señal HOLD se mantiene en alto, siempre y cuando la señal LOCK se mantenga en bajo, y con esto asegura que ningún otro procesador está tomando el bus local o que la señal HOLD que viene de las tarjetas periféricas se mantengan en nivel alto. Si cualquiera de ellas cambia, entonces otro sistema tomará el control del bus.

La señal DRQ0 es activa en alto, cuando un dispositivo externo esta listo para realizar una transferencia a través del canal 0, siempre y cuando nadie tenga el control del bus.

Para que exista una solicitud de transferencia de datos con un dispositivo externo o tarjeta periférico es necesario que la señal DMAO que viene de las tarjetas externas se active a nivel alto ó que la señal LOCK se encuentra en bajo para asegurar que nadie tiene el control del bus local. Se le da el mismo tratamiento a DRQ1.

La señal AEN se activa a nivel bajo, y está directamente conectada a la señal HOLD del microprocesador 80188, la cual le indica que desea el control del bus local para realizar un acceso directo a memoria y hacer una transferencia con un dispositivo externo a través de cualquiera de los dos canales (DMAO ó DMA1). También esta señal controla la salida del controlador del bus 8288, y

habilitador de salida(OE) de los 74LS573 para proporcionar las direcciones, y datos.

CS8251, esta señal selecciona el dispositivo externo 8251 y es activa en bajo, para direccionar este dispositivo se necesita seleccionar un puerto de entrada/salida. Esto se logra utilizando la señal PCS3 en nivel bajo.

CS8259 este dispositivo es interno a la unidad procesadora, y el control es seleccionando con la señal PCS4 en nivel bajo.

Si la señal HOLDA se mantiene en nivel alto significa que no hay una señal HOLD solicitando el control de bus local. Pero si la señal HOLDA se pone a nivel bajo; informa a las tarjetas periféricas a través de la señal HOLDA que se ha reconocido la solicitud de control del bus local y que puede empezar su proceso.

La señal CONTA es activa en nivel bajo y proporciona el control total del bus extemo, a través de la señal AEN del controlador de bus del 8288, que habilita las salidas de direcciones y datos, con el control de los habilitadores de salida (OE) de los C.I. 74LS573 y la señal DEN del C.I. 74LS645 respectivamente, siempre y cuando no exista falla en el sistema y que no se este llevando acabo una transferencia de DMA, o un reconocimiento de la señal HOLDA que controle el bus local o que la señal CEN se encuentra a nivel alto indicando que se está llevando acabo una transferencia dentro de la unidad procesadora, de memoria o un dispositivo de entrada/salida.

## V. DISQUISICIONES EXPERIMENTALES

Las ocho rutinas de prueba fueron codificadas en lenguaje ensamblador, y son las siguientes:

- 1.- Inicialización: se establecieron los parámetros y direcciones de los diferentes dispositivos periféricos internos y externos; se observó que el sistema despertó adecuadamente.

- 2.- Comunicación 8251: es útil para observar la manera en que se realizan las comunicaciones entre la CPU y las diferentes tarjetas que conforman el Multimat.

- 3.- Comunicación 8251-8259: se observó que el 8259 realizaba el control de las interrupciones correctamente.

- 4.- Memoria: se realizaron experimentos para corroborar el buen funcionamiento de los módulos de memoria de la CPU. Se enviaron informaciones por bloques de una determinada localidad de memoria a otra, y se recibieron correctamente.

- 5.- Reloj de tiempo real: se usó en experimentos relacionados con el establecimiento de la temporización necesaria para el sistema operativo MTR, el cual funcionó correctamente en rutinas de prueba.

- 6.- Transferencia DMA: se realizaron transferencias

de bloques de memoria, de una localidad a otra, a una velocidad de 2 MHz, con éxito.

- 7.- Recibe y transmite: con este programa se realizó un protocolo de comunicación para transmitir y recibir información. Todas las rutinas de prueba fueron exitosas.

- 8.- Enlace tarjeta serie: se envió información de la CPU a una de las tarjetas periféricas de entrada/salida, en modo comunicación serie. Todas las transferencias serie se realizaron correctamente.

## VI. CONCLUSIONES Y SUGERENCIAS PARA TRABAJO FUTURO

El objetivo planteado al inicio de este trabajo, a saber, sustituir la tarjeta controladora CPU del equipo de Teletransmisión Multimat del Metro de la ciudad del México por una que fuera completamente compatible y de fabricación nacional; se cumplió satisfactoriamente. A continuación se mencionan las conclusiones:

#### **VI.1 Conclusiones**

- La nueva CPU sustituye funcionalmente a la anterior.

- En virtud de que el hardware utiliza tecnología más avanzada que la CPU original, se utilizó un código más compacto, se redujo el espacio debido a que el número de dispositivos electrónicos utilizados es menor; y además, se disminuyó el costo.

- 3. La nueva CPU es de fabricación nacional.

- Respecto a las demás tarjetas de entrada/salida del Multimat, es preciso hacer notar que quedan completamente compatibles con la nueva CPU.

- La nueva CPU tiene 10 interrupciones más con respecto a la anterior, lo cual constituye una ventaja, puesto que se pueden utilizar en futuras meioras en el hardware.

- El microprocesador utilizado presenta señales directas de selección de periféricos y memorias, lo cual evita circuitería para decodificarlos.

- Se cuadruplica el espacio en memoria RAM y se duplica el espacio en memoria ROM.

- La nueva tarjeta tiene capacidad de extensión externa, para anidar una tarjeta con cuatro bloques de 8 kbytes de memoria RAM.

- La función watch dog funciona idénticamente a como funcionaba en la CPU anterior.

- Esta tarjeta presenta dos canales extras de DMA con velocidad de 2 Mbytes/seg.

- 11. La nueva tarjeta utiliza dos dispositivos más, respecto de la anterior: un controlador de bus 8288 y un controlador de interrupciones 8259.

- La nueva tarjeta tiene la capacidad de bloquear los buses de direcciones y datos cuando existe una falla, para evitar datos erróneos.

- 13. El microprocesador utilizado maneja 7 dispositivos internos, por lo que las transferencias entre estos dispositivos es más rápida y segura, minimizando las fallas.

- El microprocesador 80188 es cuatro veces más veloz que el 8088.

- La nueva tarjeta tiene una señal de sincronización hacia las tarjetas de entrada/salida para bloquear la transferencia de datos cuando existe una falla.

- Se modificó el Sistema Operativo MTR para adecuarlo a la nueva CPU.

## VI.2 Recomendaciones para trabajo futuro

Utilizar los conocimientos, las experiencias e ideas obtenidas en el diseño y construcción de la tarjeta motivo de esta tesis, para realizar otras aplicaciones de control soportadas con otras familias de microprocesadores o microcontroladores.

El proyecto presentado en esta tesis está concluido; sin embargo, queda pendiente el estudio y desarrollo de las diferentes tarjetas de entrada/salida, tanto en hardware como en software. Las nuevas tecnologías microcontroladores permiten cada vez mayor capacidad de procesamiento y velocidad, menor costo, menor tamaño, y gran facilidad de utilización tanto en hardware como en software. ofreciendo muchas ventajas y oportunidades de uso. Por estas razones creo que las tarjetas de entrada/salida que quedan pendientes de construir, se pueden desarrollar bajo este concepto.

- Respecto de la recomendación anterior, dada la complejidad del proyecto completo, se recomienda trabajar con una tarjeta a la vez, dejando idéntico el software y hardware restante.

- Queda pendiente, además, el estudio y desarrollo del conjunto completo de rutinas en lenguaje ensamblador que conformarán el nuevo BIOS y el nuevo sistema operativo.

- Las recomendaciones 2 y 3 se pueden realizar partiendo de una perspectiva completamente diferente: es posible desarrollar todo el sistema con el uso de FPGAs.

- Se pueden utilizar componentes de montaje superficial, para hacer aún más compacto el diseño.

#### VII. AGRADECIMIENTOS

Los autores agradecen el apoyo de las siguientes instituciones: Sistema de Transporte Colectivo (METRO), Secretaría Académica y COFAA del Instituto Politécnico Nacional, CONACyT y Sistema Nacional de Investigadores.

## REFERENCIAS

- David A. Patterson and John L. Hennessy (1998). Computer Organization and Design the hardware/software interface, Morgan Kaufman publishers, Inc. San Francisco, California.

- [2] J.C. Reghinot-J.C. Pianezzi (1999). Cours Practique D'Electronique, Editions Radio, Paris.

- [3] Barry B. Brey (1995). Los microprocesadores de Intel 8086 / 8088 / 80188 / 80186 / 80286 / 80388 / 80486/ Pentium, Arquitectura, Programación e Interfaces, Prentice Hall.

- [4] Mauricio Guerrero Reyes y Comelio Yáñez Márquez (1989). Diseño y Construcción de un Procesador de Propósito General., Informe Técnico No.116 Agosto, del Instituto Politécnico Nacional.

- [5] Executif Temps Reel (MTR), Systemes SA, versión 28-05-1985.

- [6] IES86 Manuel d' Utilisation (MTR) Systemes SA, versión 28-05-1985.

- [7] IES86 Guide de Configuration (MTR) Systemes SA, versión 28-05-1985...

- [8] Utilitaire RTD86 (MTR) versión 28-05-1985, Systemes SA.

- [9] EPROG Manuel de Reference (MTR) Systemes SA versión 28-05-1985.

- [10] AEDIT-80 Text Editor User's Guide (1983, 1984) Intel corporation.

- [11] PL/M-86 User's Guide (1983, 1984) Intel corporation.

- [12] ASM-86 Macro Assembler Operating Instructions (1981,1982,1983) Intel corporation.

- [13] IAPX-86,88 Family Utilities User Guide (1986) Intel corporation.

- [14] ASM86 Language Reference Manual (1986) Intel corporation.

- [15] Manuel Utilisateur "MAGUI", Sodeteg Tai.

- [16] Unidad Central Monoprocesador XM-200 (1984). Documento No. 9002388, Sodeteg Tai

- [17] 8 salidas a reles XM-204 (1984).Documento No. 9002396, Sodeteg Tai

- [18] 8 salidas a reles de mercurio XM-209 (1984). Documento No. 9002562, Sodeteg Tai

- [19] 16 entradas aisladas XM-203 (1984). Documento 9002397, Sodeteg Tai.

- [20] 40 salidas aisladas a colector abierto XM-218 (1984). Documento 9002522, Sodeteg Tai.

- [21] 24 salidas aisladas a colector abierto XM-221 (1984). Documento 9002542, Sodeteg Tai.

- [22] Enlace serie RS-232 XM-208 (1984). Documento 9002458, Sodeteg Tai.

- [23] Presentación de la Lógica Multimat Metro de México Línea A, volumen 1 y 2:Ref:TAI 04097/F03/90. Sodeteg Tai.

- [24] 16/32 Embedded processor handbook(1987) Intel corporation.

- [25] Microprocessor and Peripheral Handbook (1987), Intel corporation.

- [26] TTL Logic Data Book (1990) Texas Instrument.

- [27] M. en C. Roberto herrera Charles (1997). Tesis "Diseño del núcleo de un Sistema Operativo de Tiempo Real", CITEDI IPN, Tijuana B.C.

- [28] M. en C. Raúl espejo Rodarte (1990). Tesis "Diseño, elaboración e instalación del sistema básico de entrada/salida (BIOS) para la computadora IPN-16", CINTEC-IPN.

- [29] M. en C. Miguel Ángel López Ramírez (1999). Tesis "Desarrollo de un módulo de comunicaciones serie para el bus Multimat", CITEDI-IPN.

- [30] M. en C. Oscar Humberto Montiel Ross (1995). tesis "Diseño deuna Unidad Central de Procesamiento para Aplicaciones Industriales", CITEDI-IPN.

- [31] López-Leyva, L.O., Diaz-de-León S., J.L. & Yáñez-Márquez, C. "Equipo MULTIMAT del Sistema de Transporte Colectivo (Metro)", IT-181, Serie Azul, CIC-IPN, México, 2003.